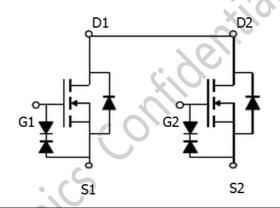

#### **Dual N-Channel Enhancement Power MOSFET**

### GENERAL DESCRIPTION

DP8810 uses advanced trench technology to provide excellent  $R_{DS(ON)}$ , low gate charge and operation with gate voltages as low as 2.5V. It is ESD protected. This device is suitable for use as a Battery protection or in other Switching application.

# **PRODUCT SUMMARY**

$V_{DS}$  20 V

$I_D$  (at  $V_{GS} = 4.5V$ ) 6.0A

$R_{DS(ON)}$  (at  $V_{GS} = 4.5V$ ) < 20m $\Omega$

$R_{DS(ON)}$  (at  $V_{GS} = 2.5V$ ) <  $25m\Omega$

ESD Rating: 2000V HBM

# ABSOLUTE MAXIMUM RATINGS (TA=25°C unless otherwise noted)

| Parameter                                           | Symbol                           | Limit      | Unit |

|-----------------------------------------------------|----------------------------------|------------|------|

| Drain-Source Voltage                                | $V_{DS}$                         | 20         | V    |

| Gate-Source Voltage                                 | $V_{GS}$                         | ±10        | V    |

| Drain Current-Continuous @ T₁=25°C                  | I <sub>D</sub>                   | 6          | А    |

| Pulsed <sup>b</sup>                                 | I <sub>DM</sub>                  | 30         | А    |

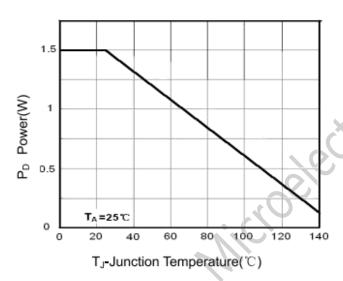

| Maximum Power Dissipation <sup>a</sup>              | P <sub>D</sub>                   | 1.5        | W    |

| Operating Junction and Storage<br>Temperature Range | T <sub>J</sub> ,T <sub>STG</sub> | -55 To 150 | ℃    |

# THERMAL CHARACTERISTIC Parameter Symbol Limit Unit Thermal Resistance, Junction-to-Ambient a Reja 100 °C/W

# **ELECTRICAL CHARACTERISTICS** (TA=25°Cunless otherwise noted)

| Parameter                               | Symbol              | Condition                                 | Min  | Турс | Max | Uni |

|-----------------------------------------|---------------------|-------------------------------------------|------|------|-----|-----|

| Off Characteristics                     |                     |                                           |      |      |     |     |

| Drain-Source Breakdown Voltage          | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V I <sub>D</sub> =250μA | 20   | -    | -   | V   |

| Zero Gate Voltage Drain Current         | I <sub>DSS</sub>    | V <sub>DS</sub> =16V,V <sub>GS</sub> =0V  | -    | -    | 1   | μΑ  |

| Gate-Body Leakage Current               | I <sub>GSS</sub>    | $V_{GS}=\pm 10V, V_{DS}=0V$               | -    | - •  | ±10 | μΑ  |

| On Characteristics                      |                     |                                           |      | X    |     |     |

| Gate Threshold Voltage                  | $V_{GS(th)}$        | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$        | 0.55 | 0.7  | 1   | V   |

|                                         | 1                   | $V_{GS}$ =4.5V, $I_D$ =6A                 | C+C  | 14   | 20  | mΩ  |

| Drain-Source On-State Resistance        | R <sub>DS(ON)</sub> | $V_{GS}$ =2.5V, $I_D$ =5A                 | -    | 17   | 25  | mΩ  |

| Forward Transconductance                | g <sub>FS</sub>     | $V_{DS}=5V,I_{D}=6A$                      | -    | 20   | -   | S   |

| Dynamic Characteristics                 |                     |                                           |      |      |     |     |

| Input Capacitance                       | C <sub>lss</sub>    | V <sub>DS</sub> =10V,                     | -    | 650  | -   | рF  |

| Output Capacitance                      | C <sub>oss</sub>    | V <sub>GS</sub> =0V,                      | -    | 140  | -   | рF  |

| Reverse Transfer Capacitance            | $C_{rss}$           | F=1.0MHz                                  | -    | 60   | -   | рF  |

| Switching Characteristics               |                     | C.                                        |      |      |     |     |

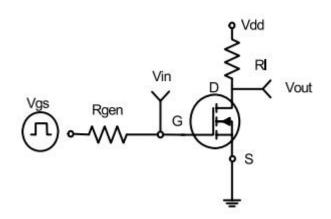

| Turn-on Delay Time                      | t <sub>d(on)</sub>  | V <sub>DD</sub> =10V,                     | -    | 0.5  | -   | nS  |

| Turn-on Rise Time                       | t <sub>r</sub>      | I <sub>D</sub> =1A                        | -    | 1    | -   | nS  |

| Turn-Off Delay Time                     | t <sub>d(off)</sub> | $V_{GS}=5V$ ,                             | -    | 12   | -   | nS  |

| Turn-Off Fall Time                      | t <sub>f</sub>      | $R_{GEN}=3\Omega$ ,                       | -    | 4    | -   | nS  |

| Total Gate Charge                       | $Q_g$               | V <sub>DS</sub> =10V,                     | -    | 8    | -   | nC  |

| Gate-Source Charge                      | $Q_{gs}$            | I <sub>D</sub> =6A,                       | -    | 2.5  | -   | nC  |

| Gate-Drain Charge                       | $Q_{gd}$            | V <sub>GS</sub> =4.5V                     | _    | 3    | -   | nC  |

| <b>Drain-Source Diode Characteristi</b> |                     |                                           |      |      |     |     |

| Diode Forward Voltage                   | $V_{SD}$            | V <sub>GS</sub> =0V,I <sub>S</sub> =1.7A  | -    | -    | 1.2 | ٧   |

| Drain-Sourse Diode Forward              | I <sub>S</sub>      | V <sub>GS</sub> =0V                       | -    | -    | 2.0 | Α   |

#### **Notes:**

- a. Surface Mounted on FR4 Board ,T<10 sec;

- b. Pulse Test: Pulse Width  $\leq$  300µs, Duty Cycle  $\leq$  2%.

- c. Guaranteed by Design, not subject to production testing.

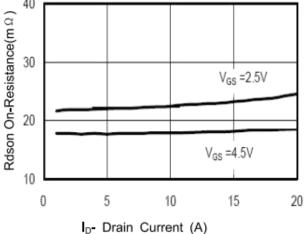

# TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

$t_{d(off)}$ **V**out INVERTED 90%  $V_{IN}$ PULSE WIDTH

**Figure 1: Switching Test Circuit**

**Figure 2: Switching Waveforms**

Figure 3: Power Dissipation

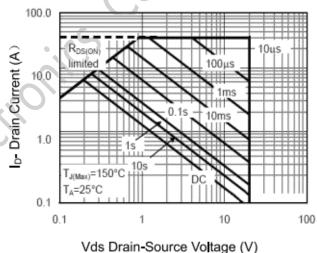

Figure 4: Safe Operation Area

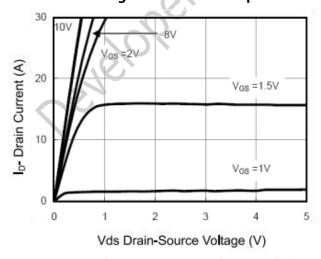

**Figure 5: Output Characteristics**

Figure 6: Drain-Source On-Rsistance

2021/6/20 DP8810 REV3.6 EN www.depuw.com

3

2021/6/20 DP8810 REV3.6 EN

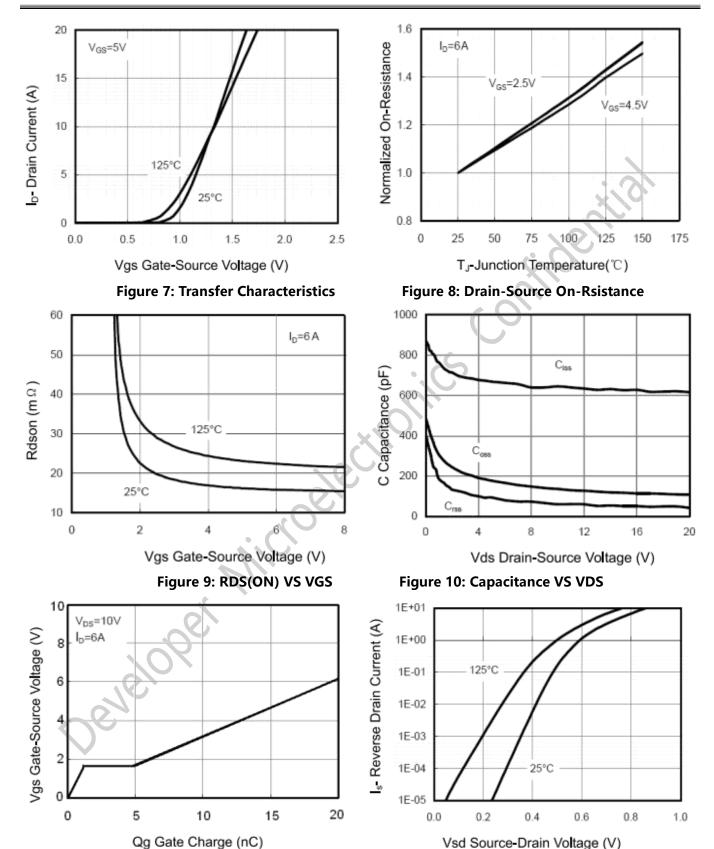

Figure 11: Gate Charge

www.depuw.com

Figure 12: Source-Drain Diode Forward

4

#### **Dual N-Channel Enhancement Power MOSFET**

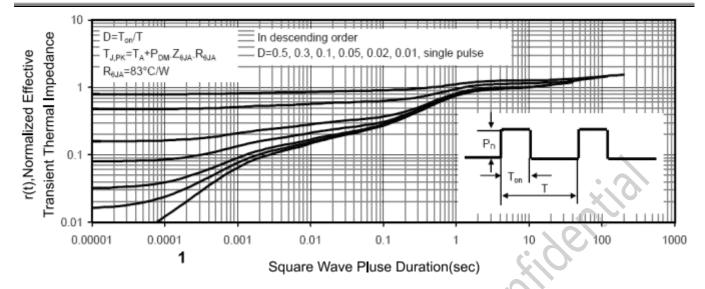

**Figure 13: Normalized Maximum Transient Thermal Impedence** Developer Microelectronics

## MARKING DESCRIPSION

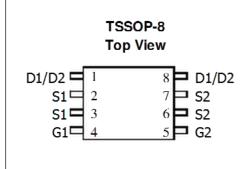

#### TSSOP-8

#### **NOTE:**

- Y —Code of productive year code(the last number of the year)

- M —Code of productive month(for example:A means January, B means February...)

- DD —Productive date(the number of the date)

- NN —Lot number of wafer

#### **FOR EXCAMPLE:**

5G1103

Means this product was produced in 2015-07-11, and 03 is the wafer lot.

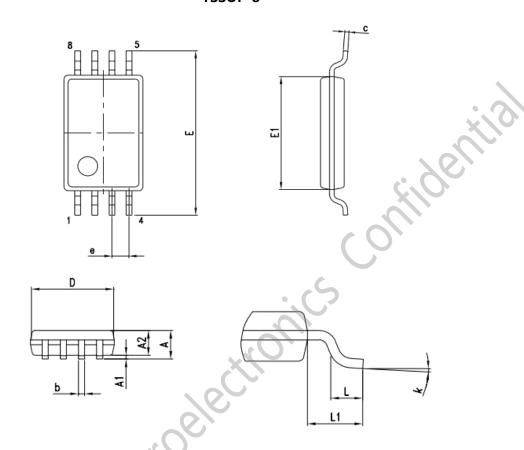

# **PACKAGE OUTLINE DIMENSIONS**

TSSOP-8

| DIM. |       | mm.  |      |       | inch. |       |  |  |

|------|-------|------|------|-------|-------|-------|--|--|

| DIW. | MIN.  | TYP. | MAX. | MIN.  | TYP.  | MAX.  |  |  |

| Α    | 1.05  |      | 1.20 | 0.041 |       | 0.047 |  |  |

| A1   | 0.05  |      | 0.15 | 0.002 |       | 0.006 |  |  |

| A2   | 0.80  |      | 1.05 | 0.032 |       | 0.041 |  |  |

| b    | 0.19  |      | 0.30 | 0.008 |       | 0.012 |  |  |

| С    | 0.090 |      | 0.20 | 0.003 |       | 0.007 |  |  |

| D    | 2.90  |      | 3.10 | 0.114 |       | 0.122 |  |  |

| E    | 6.20  |      | 6.60 | 0.240 |       | 0.260 |  |  |

| E1   | 4.30  |      | 4.50 | 0.170 |       | 0.177 |  |  |

| е    |       | 0.65 |      |       | 0.025 |       |  |  |

| L    | 0.45  |      | 0.75 | 0.018 |       | 0.030 |  |  |

| L1   |       | 1.00 |      |       | 0.039 |       |  |  |

| k    | 00    |      | 80   | 0.192 |       | 0.208 |  |  |

2021/6/20 DP8810\_REV3.6\_EN www.depuw.com

## OFFICIAL ANNOUNCEMENT

Division I will ensure the accuracy and reliability of the product specification document, but we reserve the right to independently modify the content of the specification document without prior notice to the customer. Before placing an order, customers should contact us to obtain the latest relevant information and verify that this information is complete and up-to-date. All product sales are subject to the sales terms and conditions provided by our company at the time of order confirmation.

Division I will periodically update the content of this document. Actual product parameters may vary due to differences in models or other factors. This document does not serve as any express or implied guarantee or authorization.

The product specification does not include any authorization for the intellectual property owned by our company or any third party. With respect to the information contained in this product specification, we make no explicit or implied warranties, including but not limited to the accuracy of the specification, its fitness for commercial use, suitability for specific purposes, or non-infringement of our company's or any third party's intellectual property. We also do not assume any responsibility for any incidental or consequential losses related to this specification document and its use.

We do not assume any obligations regarding application assistance or customer product design. Customers are responsible for their own use of our company's products and applications. In order to minimize risks associated with customer products and applications, customers should provide thorough design and operational safety validation.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Once discovered, the company will pursue its legal responsibility according to law and compensate for all losses caused to the company.

Please note that the product is used within the conditions described in this document, paying particular attention to the absolute maximum rating, operating voltage range, and electrical characteristics. The Company shall not be liable for any damage caused by malfunctions, accidents, etc. caused by the use of the product outside the conditions stated in this document.

Division I has been committed to improving the quality and reliability of products, but all semiconductor products have a certain probability of failure, which may lead to some personal accidents, fire accidents, etc. When designing products, pay full attention to redundancy design and adopt safety indicators, so as to avoid accidents.

When using our chips to produce products, Division I shall not be liable for any patent dispute arising from the use of the chip in the product, the specification of the product, or the country of import, etc., in the event of a patent dispute over the products including the chip.